Artificial intelligence heeft zojuist een nieuwe stap gezet in een van de meest complexe terreinen van engineering: het ontwerp van halfgeleiders. De startup Verkor.io beweert dat hun systeem Design Conductor autonoom in staat was om een volledige RISC-V CPU-kern, genaamd VerCore, te creëren op basis van een geheel van slechts 219 woorden specificatiedocument en binnen een tijdsbestek van 12 uur.

Deze uitspraak mag dan indrukwekkend klinken, maar het is belangrijk om het met nuance te lezen. Het gaat niet om dat een taalmodel een fysiek procesorchip heeft gebouwd of een CPU heeft ontworpen die vergelijkbaar is met moderne chips van Intel, AMD, Apple of Arm. Wat Verkor.io beweert, is dat hun AI-agent het volledige digitale ontwerpproces heeft doorlopen, van de initiële Specificatie tot aan een GDSII-bestand, het lay-outformaat dat wordt gebruikt in de laatste fase voor de fabricage van een geïntegreerde schakeling.

Een eenvoudige processor, maar van ontwerp tot implementatie

VerCore wordt gepresenteerd als een compatibele RISC-V kern met RV32I en ZMMUL ondersteuning, met een eenvoudige architectuur van vijf fases, in-order uitvoering en één instructie per cyclus. Volgens het technische document gepubliceerd door Verkor.io, behaalde het ontwerp een kloksnelheid van 1,48 GHz met behulp van ASAP7, een academisch voorspellend procesontwerp-kit voor 7 nm, en behaalde een CoreMark-score van 3.261, een gangbare test voor het meten van prestaties van microcontrollers en embedded CPU’s.

Het rapport vergelijkt dit resultaat met dat van een Intel Celeron SU2300 uit 2011, een behoorlijk bescheiden processor, zelfs voor de maatstaven van meer dan tien jaar geleden. Deze vergelijking plaatst de vooruitgang in perspectief: VerCore is geen concurrent voor moderne processoren en heeft dat ook niet als doel. Het belang ligt in het proces, niet zozeer in de uiteindelijke kracht van de chip.

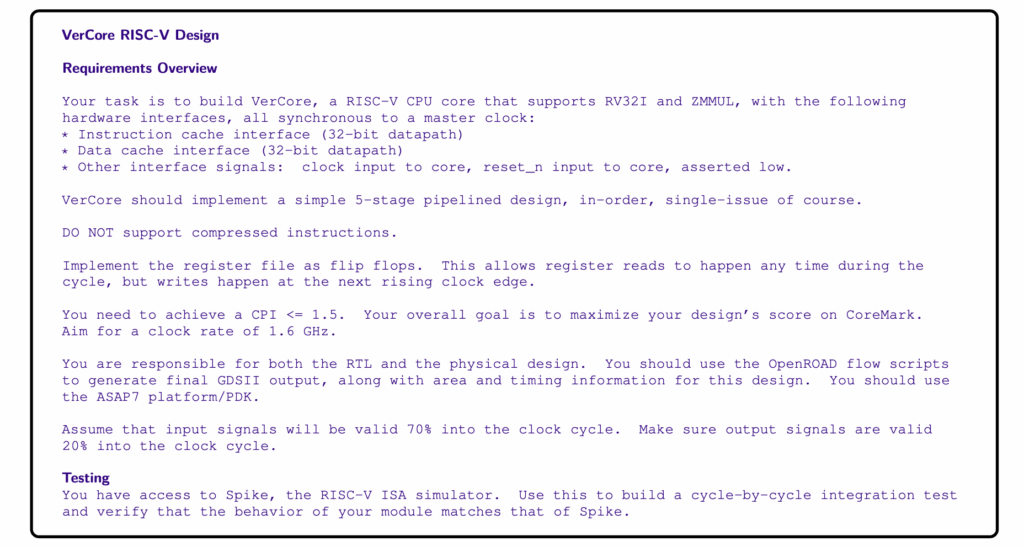

Design Conductor is geen strikt geïsoleerd AI-model, maar een orkestratietool die geavanceerde modellen begeleidt bij het uitvoeren van ontwerp-, review-, debug- en optimalisatietaken. In dit geval kreeg het systeem een korte specificatie waarin werd gevraagd om een RISC-V CPU met instructiecache-interface, datacache-interface, vijflagen pipelined ontwerp, ondersteuning voor RV32I en ZMMUL, geen gecomprimeerde instructies en een CPI-doel van gelijk aan of lager dan 1,5.

Van daaruit genereerde de agent voorstellen voor microarchitectuur, implementeerde modules in Verilog, creëerde testbanken, vergeleek het gedrag van de processor met Spike — de referentie-simulator voor RISC-V —, debugde functionele fouten en paste het fysieke ontwerp aan met behulp van electronic design automation (EDA) tools.

Het belang van GDSII en de kritische nuance: nog niet gerealiseerd

De stap naar GDSII is cruciaal omdat dat bestand de fysieke lay-out van de chip vertegenwoordigt, dat wil zeggen, een ontwerp dat klaar is voor de laatste fases van fabricage. In traditioneel chipontwerp vereist dat architecten, RTL-ingenieurs, verificatiespecialisten, timing-experts, backend-teams en complexe EDA-flows samenwerken om dat punt te bereiken.

Het document van Verkor.io benadrukt dat de ontwikkeling van een geavanceerde chip meer dan 400 miljoen dollar kan kosten en 18 tot 36 maanden kan duren, met teams van honderden ingenieurs. Gezien die context is het opmerkelijk dat een AI-agent een werkbaar en verificeerbaar ontwerp kon voltooien in slechts 12 uur, al is het hier om een relatief eenvoudige CPU te gaan.

De belangrijkste voorzichtigheid is dat VerCore nog niet is gefabriceerd. Het ontwerp is bevestigd via simulaties en geïmplementeerd op ASAP7, een academisch PDK ontwikkeld door de Arizona State University in samenwerking met ARM Research. Dit betekent dat het resultaat geen commerciële chip is die klaar is voor de markt, maar een technische demonstratie van een geautomatiseerd ontwerpproces.

Verder is het belangrijk te realiseren dat verificatie voor massaproductie veel strenger is dan het slagen in functionele tests of benchmarks in simulatie. In de halfgeleiderindustrie kan een fout die na tape-out wordt gevonden enorme kosten met zich meebrengen. Daarom vormt verificatie vaak een groot deel van de totale ontwikkelingsinspanning.

Wat brengt AI in chipontwerp?

Het meest interessante aspect van Verkor.io’s werk ligt in hoe de agent lijkt te werken volgens een methodologie die lijkt op die van een teamsamenwerking: ontwerpen, testen, fouten detecteren, corrigeren en opnieuw meten. Het rapport beschrijft bijvoorbeeld hoe Design Conductor VCD-tracés analyseerde, simulatiegegevens naar CSV-bestanden converteerde, schrijffouten in registers opspoorde en problemen in het pipeline-vullingslogica na sprongen corrigeerde.

Het systeem onderzocht ook varianten in microarchitectuur. Volgens het document probeerde het ontwerpen uit met penalty voor sprongen van één en twee cycli, implementeerde het vroege forwarding en kwam het tot een oplossing met een Booth-Walling multipliator van vier fasen. Niet alle beslissingen waren in de oorspronkelijke specificatie vastgelegd, wat wijst op een zekere exploratie binnen een meetbaar doel.

Toch erkent het rapport ook belangrijke beperkingen. Modellen kunnen niet altijd perfect redeneren over Verilog, en verwarren soms het gedrag van hardware met dat van een sequentieel programma, waardoor suboptimale beslissingen worden genomen die later moeten worden gecorrigeerd op basis van timingrapporten. Met andere woorden: AI kan het proces versnellen, maar nog steeds is een menselijke expert nodig om richtingen te sturen en juiste beslissingen te nemen.

RISC-V als natuurlijk terrein voor experimenten

De keuze voor RISC-V is geen toeval. Het is een open, modulair instructieset-architectuur, beheerd door RISC-V International, die bijzonder aantrekkelijk is voor onderzoek, onderwijs, microcontrollers, op maat gemaakte ontwerpen en nieuwe gespecialiseerde chips.

De openheid vergemakkelijkt dat universiteiten, start-ups en bedrijven kunnen experimenteren met nieuwe cores zonder de licentiebaarheid die gepaard gaat met propriëtaire architecturen. In combinatie met open source tools zoals OpenROAD en academische kits zoals ASAP7, biedt RISC-V een ideaal platform om de grenzen van geautomatiseerd hardware-ontwerp te verkennen.

Het precedent dat VerCore schetst, komt niet uit de lucht vallen. In de laatste jaren zijn er al experimenten geweest met AI toegepast op digitale synthese, Verilog-generatie en het ontwerp van eenvoudige circuits. Wat volgens Verkor.io nieuw is, is dat deze capaciteiten nu verbonden worden in één volledige workflow, van specificatie tot GDSII-layout van een werkende CPU.

De volgende stap is het verifiëren of andere ingenieurs het resultaat kunnen reproduceren. Verkor.io heeft aangekondigd de relevante ontwerpbestanden vrij te geven, zodat derden het RTL, scripts en het bouwproces kunnen nakijken. Ook is de planning om een FPGA-implementatie van VerCore te tonen op de Design Automation Conference in Long Beach, in juli.

De boodschap moet dus niet worden opgevat als de aankondiging van een revolutionaire CPU, maar als een indicatie van de mogelijke richting waarin halfgeleiderengineering zich beweegt. Als deze systemen zich verder ontwikkelen, kunnen ze de ontwerptijd verkorten, meer varianten mogelijk maken en kleine teams in staat stellen om projecten aan te pakken die tegenwoordig enorme resources vereisen. Maar de sprong van een academische demonstratie tot een betrouwbare, commerciële chip blijft een grote uitdaging.

Veelgestelde vragen

Wat is VerCore?

VerCore is een RISC-V CPU-kern ontworpen door het agentgebaseerde AI-ontwerpsysteem Design Conductor van Verkor.io. Het is een eenvoudige 32-bits processor met een vijffase architectuur, in-order uitvoering en ondersteuning voor RV32I en ZMMUL.

Is VerCore al gefabriceerd als fysiek circuit?

Neen. Volgens beschikbare informatie is VerCore gevalideerd in simulatie en tot aan een GDSII-bestand ontwikkeld, maar is het nog niet fysiek gemaakt als een commerciële chip of siliciumprototype.

Wat betekent het dat een AI tot GDSII is gekomen?

Het betekent dat het systeem een fysieke lay-out van het circuit heeft gegenereerd, een gevorderde fase in chipontwerp. Maar het bereiken van GDSII garandeert op zichzelf niet dat de chip klaar is voor massaproductie; extra validaties en industriële processen zijn nog nodig.

Kan AI chips ontwerpen vervangen?

Voorlopig niet. Dit geval illustreert dat AI delen van het ontwerp kan automatiseren en het onderzoeken van alternatieven kan versnellen, maar nog altijd blijven architecten en ervaren ingenieurs essentieel voor het begeleiden, controleren en valideren van complexe ontwerpen.