De halfgeleiderindustrie blijft doorgaan met ontwikkelingen, maar elke nieuwe sprong vereist meer tijd, meer investeringen en grotere architectuurwijzigingen. Het ouderwetse idee dat transistors simpelweg kleiner werden van generatie tot generatie past niet meer bij de realiteit. In het tijdperk van angstroms zal verbetering komen uit een veel complexere mix: nieuwe transistortechnologieën, verticale stacking, alternatieve materialen, fijnere interconnecties, voeding vanaf de achterzijde van de wafer en geavanceerde packaging.

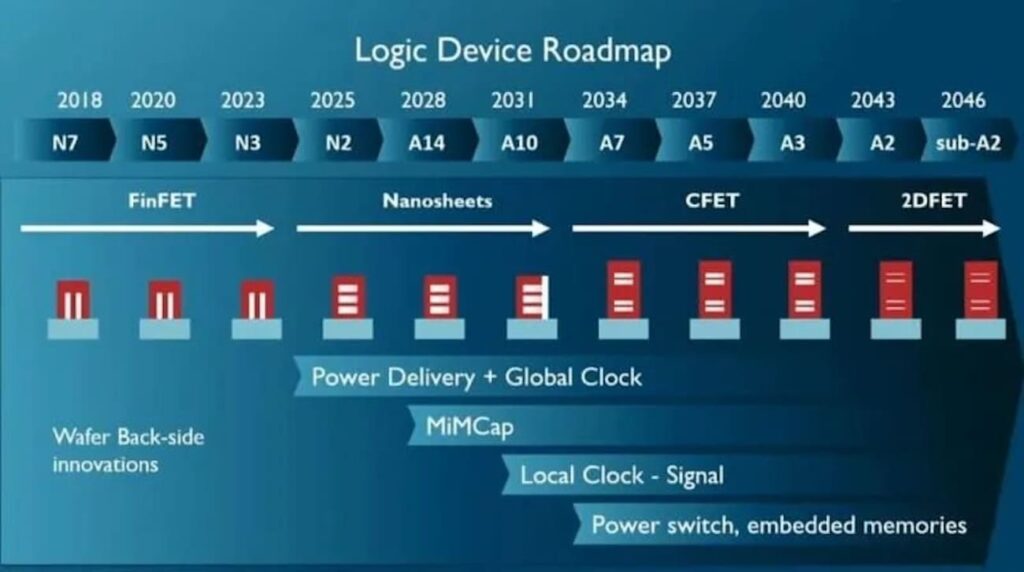

De routekaart die aan imec, het Belgische onderzoekscentrum voor nano-elektronica, wordt toegeschreven, plaatst de eerste node onder de 1 nm rond 2034. Dit punt zou verbonden zijn met de A7-node, ongeveer 0,7 nm of 7 angstroms, en markeert de toetreding van CFETs, een architectuur waarbij n en p kanaal-transistors vertical worden gestapeld om de logische dichtheid verder te verhogen. Later, rond 2043, zouden 2D FETs in de A2-node verschijnen, met tweedimensionale materialen als een mogelijke weg om de miniaturisering verder te brengen voorbij de huidige limieten.

Een belangrijke correctie: deze cijfers moeten niet worden gelezen als een garantie voor exacte commerciële productie. In de halfgeleiderindustrie beschrijven de knooppunten niet langer letterlijk fysieke afmetingen van de transistors, maar zijn het labels voor technologische en commerciële marktsegmenten. De routekaart schetst alleen onderzoeks- en ontwikkelingsfasen, niet noodzakelijk dat een specifieke fabrikant in 2034 chips van 0,7 nm zal kunnen verkopen of dat die van 0,2 nm in 2043 realiteit worden. Toch helpt het tijdschema om de richting van de sector te begrijpen.

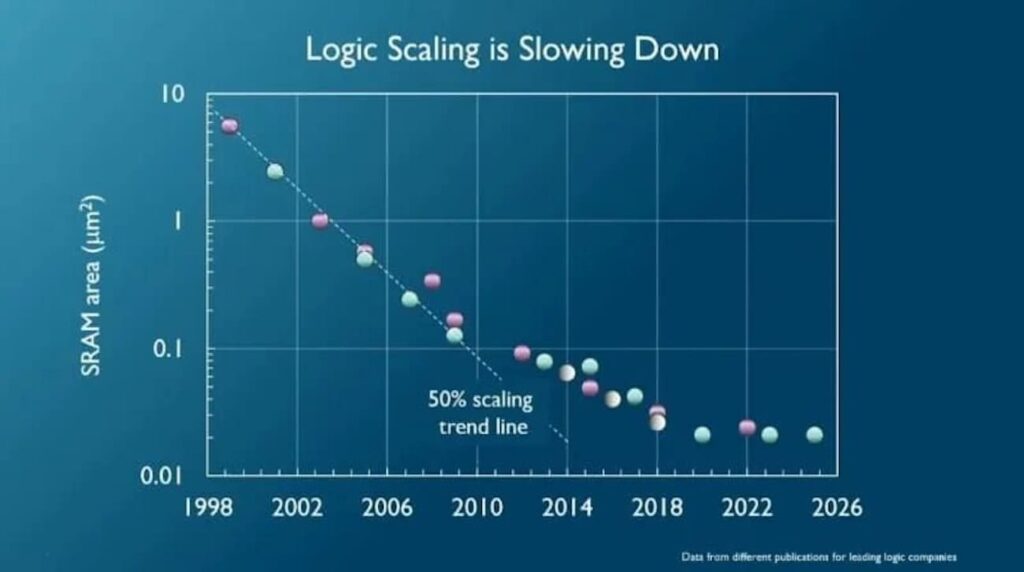

Moore bestaat nog, maar het gaat niet meer hetzelfde

Decennialang leunde de industrie op agressieve technologische reducties in de grootte van transistors. Van eind jaren negentig tot begin jaren 2000 verbeterde de logische dichtheid zo snel dat het mogelijk was prestaties te verdubbelen of kosten te verlagen met elke nieuwe generatie. Deze dynamiek is afgezwakt. De verkleining van het areaal van SRAM-cellen, een belangrijke indicator voor schaalbaarheid van knooppunten, is al jaren afgenomen in snelheid, en bij recente nodes verloopt de verbetering veel minder spectaculair.

Het probleem ligt niet alleen in de fysieke beperkingen. Fabricage in geavanceerde knooppunten vereist geavanceerde EUV-lithografie, meer complexe processen, meer maskers, meer fabricagestappen en enorme investeringen in fabrieken. Daarom wenden grote chipfabrikanten en ontwerpers zich steeds meer tot chiplets, 2,5D, 3D IC, interposers en geavanceerd packaging. In plaats van alles te integreren op één gigantisch die, worden gespecialiseerde blokken gemaakt in verschillende knooppunten en via steeds verfijnder technieken aan elkaar gekoppeld.

AI en high-performance computing versnellen deze trend. Moderne accelerators hangen niet alleen af van kleinere transistors; ze vereisen ook dicht bij de processor HBM-geheugen, high-bandwidth interconnects, efficiënte spanningsvoorziening en thermisch beheer. De race is niet alleen voor het knooppunt, maar voor het hele systeem.

Desondanks blijft logica verder schaalbaar. De routekaart voorziet een duidelijke overgang van FinFET naar nanosheets, daarna CFETs en later transistors gebaseerd op 2D-materialen. Elke sprong probeert hetzelfde dilemma op te lossen: hoe de dichtheid en prestaties verhogen wanneer horizontale verkleining niet meer volstaat.

| Geschatte periode | Knooppunt | Voorspelde architectuur | Belangrijkste concept |

|---|---|---|---|

| 2018-2023 | N7, N5, N3 | FinFET | Laatste grote FinFET fase in geavanceerde knooppunten |

| 2025 | N2 | Nanosheet / GAA | Introductie van gate-all-around transistors |

| 2028 | A14 | Verbeterde nanosheets | Meer dichtheid en architectuuraanpassingen |

| 2031 | A10 | Geavanceerde nanosheets | Laatste fase vóór sub-1 nm |

| 2034 | A7 | CFET | Eerste knooppunt onder 1 nm |

| 2037 | A5 | Verbeterde CFET | Meer verticale schaalvergroting en optimalisaties |

| 2040 | A3 | Geavanceerde CFET | Uitbreiding CFET-architectuur |

| 2043 | A2 | 2D FET | Invoering van tweedimensionale materialen |

| 2046 | Sub-A2 | Geavanceerde 2D FET | Scenario voor volledige doorontwikkeling voorbij 0,2 nm |

CFET en 2D FET: de strategie van stapelen en nieuwe materialen

De eerstvolgende grote stap is al in gang gezet met nanosheet FETs, ook bekend als GAA (gate-all-around). Het idee is om het kanaal van de transistor rondom de hele omtrek door de poort af te schermen, wat meer controle geeft in vergelijking met FinFET. TSMC, Samsung en Intel werken aan eigen varianten van deze overgang, elk met eigen benamingen en kalenders.

De volgende grote ontwikkeling zou CFET zijn. In een CFET-architectuur worden nMOS- en pMOS-transistors verticaal gestapeld in plaats van naast elkaar. Hiermee kan areaal worden verminderd en kan dióden dichtheid toenemen, los van het maken van alles kleiner. Imec heeft in technische publicaties aangegeven dat CFET een aantrekkelijke architectuur is voor knooppunten onder 1 nm en heeft geëxploreerd met verschillende integratietechnieken, waaronder monolithische en sequentiële stacking.

De daaropvolgende sprong is de invoering van 2D FETs. Hier gaat het niet alleen om reorganisatie van siliciumtransistors, maar om het gebruik van 2D-materialen in de kanalen. Het voordeel is dat deze materialen hun elektrische kenmerken behouden op zeer kleine schalen. De uitdaging ligt in de industrialisatie: het verkrijgen van productiedoorvoer, uniformiteit, goede contactpunten en betrouwbaarheid. Hoewel onderzoek veelbelovend is, bevinden massaproductiemethoden zich nog in een ontwikkelingsfase, en blijven er technische obstakels te overwinnen.

Daarom moet het horizon 2043-2046 met voorzichtigheid worden benaderd. Het is geen vaste productlancering, maar een onderzoeksvisie die de mogelijke stappen aangeeft, mits de industrie erin slaagt materialen, procestechnologieën, interconnecties, voeding en koeling te verbeteren.

De knelpunten in verbindingen en téken

Het verkleinen van transistors is niet genoeg als de verbindingen tussen transistors de nieuwe bottleneck worden. De BEOL-laag, verantwoordelijk voor de metallagen die componenten verbinden, is één van de kritischste zones. Naarmate pitches afnemen, nemen weerstand, congestie en thermische problemen toe. Koper – jarenlang de standaard – krijgt het moeilijk op zeer kleine schaal vanwege barrières en volumeverlies.

De routekaart wijst op een geleidelijke overgang naar materialen zoals ruthernium en technieken zoals semi-damascene en subtractieve metallisatie, samen met air gaps en zelfuitgelijnde vias. Tegen ongeveer 2 nm knooppunten worden minimale pitches tussen 24 en 26 nm verwacht; bij A14 dalen ze naar 20-22 nm; bij A10 rond 18-20 nm; en voor A7 zou dat onder andere 16-18 nm kunnen worden. Voor A5 en A3 ligt de doelstelling tussen 12 en 16 nm, al bevinden die zich nog in onderzoeksstadia.

| Geschatte Jaar | Knooppunt | Minimaal metall-pitch | Uitstekende BEOL-technologie |

|---|---|---|---|

| 2025 | N2 | 24-26 nm | Koper, dual/single damascene |

| 2028 | A14 | 20-22 nm | Verbeteringen bestaande processen |

| 2031 | A10 | 18-20 nm | Overgang naar ruthernium, air gaps en zelfuitgelijnde vias |

| 2034 | A7 | 16-18 nm | Semi-damascene / subtractieve metallisatie |

| 2037 | A5/A3 | 12-16 nm | Alternatieve materialen in onderzoek |

Hier wordt zelden publiek over gesproken omdat men zich vaak richt op zogenoemde “knopen van 2 nm” of “1,4 nm”, maar het is van cruciaal belang. Een chip wordt niet beter alleen doordat transistors meer dense worden. Als voedingslijnen, signalen en warmtebeheer niet meeschuiven, wordt de prestatie beperkt of loopt het energieverbruik uit de hand.

Achterwaartse voeding en het warmteprobleem

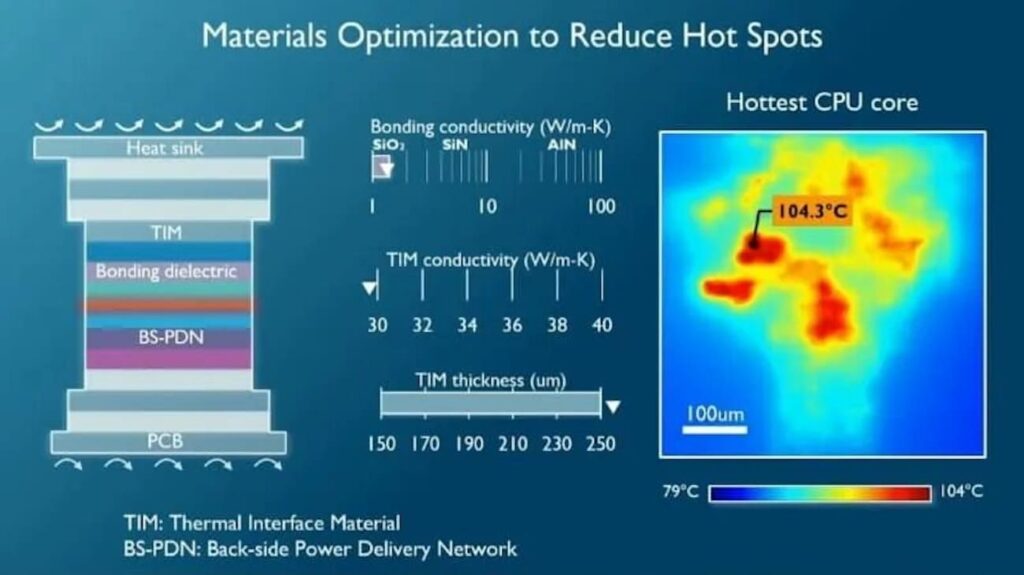

Een andere belangrijke factor is de voeding. Traditioneel worden signalen en energie via de voorkant van de wafer geleid, wat veelvuldig ruimte eist in metalen lagen. Het achterwaartse voeden, de backside power delivery network (BSPDN), scheidt deze voeding en creëert ruimte aan de voorkant voor signalen. Het potentieel is groot: minder congestie, betere stroomvoorziening en meer schaalmogelijkheden.

Maar het brengt ook uitdagingen met zich mee. Het veranderen van de voedingsroute beïnvloedt de thermische paden en kan de koeling bemoeilijken. Imec waarschuwt dat het ontwerp en de thermische afwegingen zorgvuldig moeten worden afgewogen. In high-performance chips, waar warmte al een grote beperkende factor is, betekent elke fysieke verandering grote gevolgen.

De routekaart vermeldt ook integratie van spanningsregelaars in de print, het pakket, de interposer of zelfs de achterkant van de wafer. In AI- en HPC-systemen, waar chips met meerdere chiplets, HBM en accelerators worden samengevoegd, is een precieze elektrische architectuur essentieel. Voeding wordt onderdeel van het systeemontwerp, niet alleen een externe factor.

Dit is de echte boodschap achter de routekaart: de toekomst van halfgeleiders hangt niet af van één magisch technologiehoogtepunt, maar van de coordinatie van nieuwe transistortechnologieën, efficiëntere bekabeling, energiebeheer, materialen, 3D-packaging, nabijgelegen geheugen en warmteafvoer. Miniaturisering gaat door, maar niet meer vanzelf.

Als de voorspellingen uitkomen, zal de komst van chips onder 1 nm geen simpel knooppuntverandering zijn. Het zal het resultaat zijn van bijna tien jaar voorbereidingstechniek, van de huidige nanosheets naar CFETs en daarna 2D-materialen. Tegelijkertijd moet de industrie elk sprongetje economisch verantwoorden, zeker nu fabrieken fors duurder worden en actiever gebruik wordt gemaakt van geavanceerd packaging. Niet elk product zal het ultieme knooppunt nodig hebben.

Grote AI-versnellers, HPC-processors en datacenterschips zullen de grens blijven verleggen. De rest van de markt zal waarschijnlijk een mix worden van volwassen knooppunten, chiplets en geavanceerd packaging, om kosten en prestaties in balans te houden. Moore leeft nog, maar het wordt steeds duurder, verticaler en complexer om in één getal in nanometers te vatten.

Veelgestelde vragen

Wanneer zullen chips onder de 1 nm beschikbaar zijn?

De routekaart van imec wijst op de eerste knooppunten onder de 1 nm rond 2034, met A7 oftewel 0,7 nm gebaseerd op CFET-technologie. Dit is geen garantie voor een direct commercieel product.

Wat is een CFET?

Een CFET is een type transistor waarbij n en p kanaaltransistors verticaal worden gestapeld, wat de logische dichtheid verder verhoogt.

Wat zijn 2D FETs?

Transistors die materialen gebruiken met twee dimensies in het kanaal, bedoeld om logische schaalvergroting te blijven ondersteunen tot onder de 0,2 nm.

Waarom is het verminderen van transistorformat niet meer voldoende?

Omdat de beperkingen nu ook liggen in interconnectie, voeding, warmteafvoer, geheugen en productiekosten. Het volledige systeemontwerp wordt steeds bepalender voor de prestaties.

bron: 36kr