La próxima gran batalla en la memoria para la Inteligencia Artificial podría no decidirse únicamente por capacidad o ancho de banda, sino por la forma de unir físicamente cada capa del chip. Esta es la conclusión del nuevo análisis de Counterpoint Research, que prevé que SK hynix adoptará hybrid bonding para HBM5 y que esta generación llegará al mercado alrededor de 2029-2030, en paralelo con el próximo gran ciclo de GPUs para IA. Según la firma, este avance marcaría la transformación de la unión híbrida desde una tecnología prometedora a una fase de producción a gran escala en el mercado de HBM.

La hipótesis de Counterpoint no surge de la nada. En marzo de 2026, Applied Materials y SK hynix anunciaron una alianza de I+D a largo plazo para acelerar innovaciones en DRAM de próxima generación y HBM, con colaboración en materiales, integración de procesos y empleo avanzado de packaging en el nuevo EPIC Center en Silicon Valley. Applied también explicó que estos programas iniciales buscarán explorar nuevos materiales, esquemas complejos de integración y soluciones de empaquetado específicas para HBM, con el objetivo de mejorar tanto el rendimiento como la fabricabilidad en futuras arquitecturas de memoria.

En este escenario también entra BESI. Applied describe su sistema Kinex como una plataforma de hybrid bonding die-to-wafer desarrollada junto con BE Semiconductor Industries, diseñada para entornos de fabricación de alto volumen y optimizada para aplicaciones como HBM, circuitos 3D y opto-empaquetado co-integrado. La compañía destaca que este sistema integra limpieza húmeda, activación por plasma y metrología en línea para controlar el superposicionamiento (overlay) y el rendimiento, elementos que se vuelven críticos cuando la industria busca escalar el empaquetado avanzado hacia producción masiva.

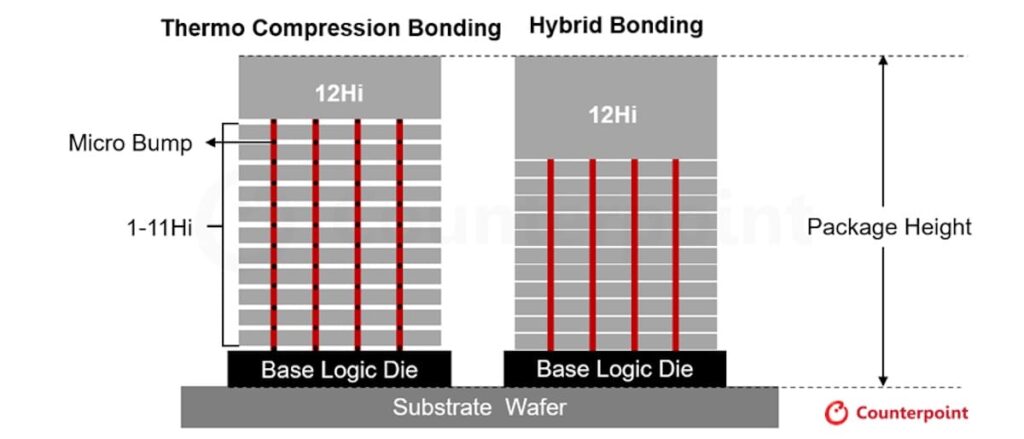

El aspecto técnico del asunto es conocido, aunque cada vez más apremiante. El HBM actual todavía se apoya en gran medida en microbumps y en procesos como thermo-compression bonding, una solución que ha funcionado hasta ahora, pero que empieza a mostrar límites a medida que aumentan las pilas, disminuye el pitch y las exigencias en potencia, altura y eficiencia térmica crecen. Counterpoint argumenta que la unión híbrida ofrece ventajas estructurales claras: interconexiones más finas, menor separación entre dados, menor altura total y mejor eficiencia energética. En otras palabras, no se trata solo de una mejora en el packaging, sino de un cambio de arquitectura industrial para seguir escalando el HBM más allá de las generaciones actuales.

Lo interesante es que SK hynix ya está preparando el terreno para una transición comercial, aunque todavía no lo haya comunicado oficialmente como una hoja de ruta definida hacia HBM5. En su comunicación pública de 2026, la compañía ha dejado claro que su foco inmediato está en HBM3E y HBM4, dos familias que considera fundamentales para el superciclo de memoria para IA. En MWC 2026, por ejemplo, mostró HBM4 para plataformas de centros de datos de próxima generación, con 2.048 I/Os, más del doble de ancho de banda comparado con la generación anterior y una mejora de más del 40 % en eficiencia energética, además de su oferta de DDR5 y módulos diseñados para entornos de IA y servidores.

Esto sugiere que la ventana 2029-2030 que plantea Counterpoint encaja con una estrategia por fases: primero, HBM4 y la expansión del ecosistema AI a corto plazo, y posteriormente una HBM5 donde el packaging híbrido no sería solo una innovación de laboratorio, sino un requisito industrial para seguir aumentando densidad, ancho de banda y eficiencia. En ese escenario, la ventaja competitiva no residirá solo en la calidad de las celdas DRAM, sino en la capacidad de integrar materiales, pulido químico-mecánico, control de superficie, bonding y rendimiento en una misma cadena de fabricación.

Counterpoint también señala un elemento estratégico que va más allá del proceso: la escasez estructural de memoria para IA. La firma advierte que la aceleración en la adopción de IA podría intensificar los cuellos de botella en la cadena de suministro hasta finales de la década, con 2028 como posible punto de inflexión, cuando entren en operación nuevos clusters de producción. Desde esta perspectiva, adelantar la adopción del hybrid bonding no solo tiene implicaciones técnicas, sino también comerciales: quien domine esa transición estará mejor posicionado para proteger márgenes, rendimiento y cuota de mercado en un segmento donde la demanda crece más rápido que la capacidad de producción.

Por ahora, la gran incógnita no es si la industria terminará adoptando hybrid bonding en HBM, sino cuándo. Counterpoint considera que HBM5 será el verdadero catalizador. Applied ya está hablando de herramientas específicamente optimizadas para HBM y producción en volumen. Y SK hynix está posicionándose mediante alianzas, exhibiciones de HBM4 y una estrategia clara para sostener el superciclo de memoria para IA. La conclusión es bastante clara: aunque aún no exista un anuncio oficial de un “HBM5 híbrido”, la tendencia empieza a delinearse con bastante claridad.

Preguntas frecuentes

¿SK hynix ha confirmado oficialmente que HBM5 usará hybrid bonding?

No de forma pública ni oficial. Actualmente, solo existe una previsión de Counterpoint Research que Sitúa esa adopción en 2029-2030, junto con otros movimientos en la industria que apuntan en esa dirección.

¿Qué papel juegan Applied Materials y BESI en esta historia?

Applied y SK hynix ya han anunciado una alianza para I+D en próxima generación de DRAM y HBM; además, Applied comercializa Kinex, una plataforma de hybrid bonding desarrollada junto con BESI, optimizada para HBM y otras aplicaciones avanzadas.

¿Por qué es tan importante el hybrid bonding para HBM5?

Porque permite pitches más finos, menor altura de pila, mejor eficiencia energética y mayor ancho de banda en comparación con las soluciones basadas en microbumps, lo cual es esencial a medida que el HBM escala en número de capas y requisitos térmicos.

¿Cuál es la hoja de ruta pública más próxima de SK hynix?

La compañía está enfocada en HBM3E y HBM4 como impulsores del actual superciclo de memoria para IA. En MWC 2026 presentó un HBM4 con 2.048 I/Os, doble ancho de banda y más de un 40 % de mejora en eficiencia energética.

vía: korea.counterpointresearch