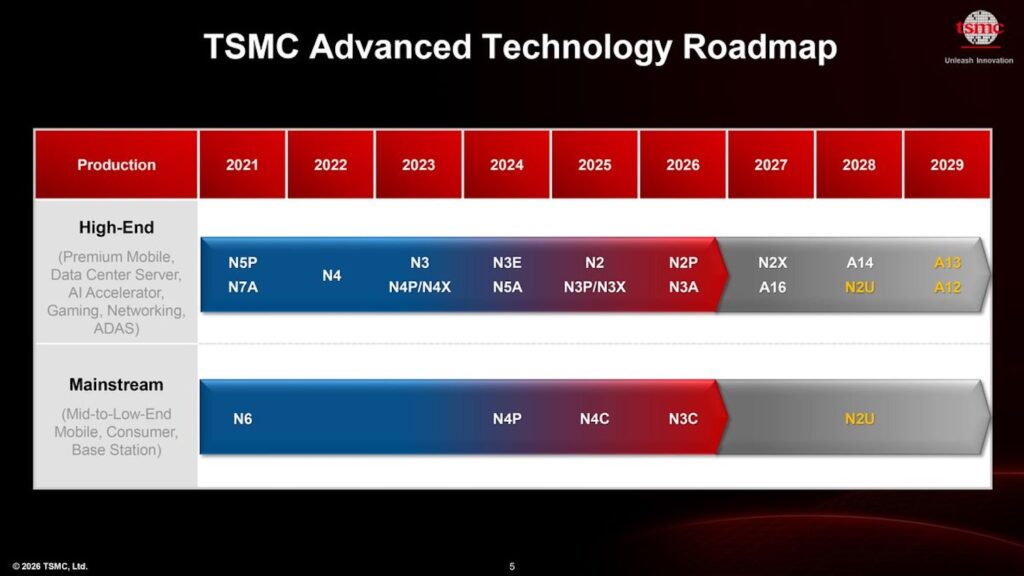

TSMC heeft tijdens zijn Technology Symposium 2026 een routekaart gepresenteerd die aanzienlijk verder gaat dan een eenvoudige incrementale update. Het Taiwanese bedrijf heeft een duidelijke planning en vorm gegeven aan de volgende fase van zijn aanval op geavanceerde logica, automotive en AI-pakketvorming, met een opeenvolging die niet langer beperkt is tot bekende namen zoals N2, A16 en A14, maar nu ook nieuwe onderdelen omvat zoals N2U, A13, A12, N2A en een zeer agressieve uitbreiding van CoWoS, SoW-X en SoIC. De boodschap is helder: TSMC wil niet alleen vooroplopen op het gebied van halfgeleiderfabrieken, maar ook op het gebied van geheugenintegratie, 3D-stapeling en systeemdichtheid.

Het meest belangrijke aspect van de aankondiging is niet alleen dat TSMC blijft innoveren, wat al verwacht werd, maar vooral hoe het zijn tijdlijn tot 2029 heeft gestructureerd. Het bedrijf heeft de ‘standaard’ evolutie en de achterzijde-voeding (backside power delivery) beter onderscheiden, terwijl het zich versnelt in pakketvorming om te reageren op de werkelijke marktdruk van AI. Gezamenlijk versterkt de nieuwe routekaart de indruk dat TSMC niet alleen voorop wil lopen bij procesnoden, maar ook op het vlak van geheugenintegratie, vertical stacking en systeemdichtheid, en daarmee niet alleen concurrenten zoals Intel en Samsung wil aanstoten, maar ze ook wil dwingen tot gelijktijdige competitie op meerdere fronten: proces, vermogen, geheugen en integratie.

N2U, A13 en A12: een meer gedifferentieerde routekaart

De eerste belangrijke nieuwe ontwikkeling is N2U, een nieuwe uitbreiding van de 2 nm-platformlijn. Volgens TSMC is dit knooppunt geoptimaliseerd via gezamenlijke ontwerp- en technologische verfijningen en biedt het tussen 3 % en 4 % hogere snelheden of tussen 8 % en 10 % lager energieverbruik in vergelijking met N2P, naast een logische dichtheidstoename van 1,02x tot 1,03x. Het wordt gepositioneerd als een gebalanceerde keuze voor AI, HPC en mobiel, ondersteund door de volwassenheid en fabricageprestaties van de 2 nm-platforms, met productie gepland voor 2028.

Naast deze evolutie kondigt TSMC ook A13 officieel aan, dat een directe shrink van A14 is. Op papier biedt A13 een 6 % besparing in oppervlakte ten opzichte van A14, behoudt volledige compatibiliteit met ontwerpregels en implementeert verbeteringen in energie-efficiëntie en prestatie via gezamenlijke optimalisatie. De productie is gepland voor 2029, een jaar na A14. Die compatibiliteit in ontwerp is niet onbelangrijk omdat het klanten eenvoudiger maakt om migraties te maken zonder grote ruptuur met de vorige generatie.

De derde ontwikkeling in deze geavanceerde tak is A12, dat TSMC presenteert als een upgrade van de A14-omgeving, ontworpen voor AI en HPC door middel van Super Power Rail, een technologie voor stroomvoorziening via de achterzijde van de chip. TSMC positioneert A12 als een volgende stap in het aanpakken van een van de grootste knelpunten bij siliconen: het efficiënt leveren van stroom bij steeds hogere dichtheden en stroombehoeften. Ook voor A12 staat productie gepland voor 2029.

Tabel: Het nieuwe routekaart van TSMC tot 2029

| Technologie | Focus | Verwachte datum |

|---|---|---|

| N2U | Verbeterde 2 nm-ontwikkeling met balans tussen snelheid, verbruik en dichtheid | 2028 |

| A13 | Shrink van A14 met 6 % minder oppervlak en compatibele regels | 2029 |

| A12 | Platform met Super Power Rail voor AI en HPC | 2029 |

| N2A | Eerste automotive-knooppunt met nanosheets | 2028 (AEC-Q100 gecertificeerd) |

| CoWoS 14-reticles | Tot ~10 grote reken-chips en 20 HBM-stapelingen | 2028 |

| CoWoS >14-reticles | Uitbreiding van pakketvorming | 2029 |

| SoW-X | wafer-omvattende integratie met meer dan 40 reticles | 2029 |

| A14-to-A14 SoIC | 3D-stapeling met 1,8x meer E/S dichtheid die-die tot die | 2029 |

Bron: TSMC North America Technology Symposium 2026.

Automotive en fysieke AI: TSMC beweegt ook met N2A

TSMC beperkt de discussie niet tot mobiel en datacenters. Tijdens hetzelfde evenement kondigde het bedrijf N2A aan, beschreven als zijn eerste automotive-proces met nanosheet-transistors. Het bedrijf stelt dat N2A tussen 15 % en 20 % hogere snelheden kan leveren met hetzelfde verbruik in vergelijking met N3A en dat het in 2028 de AEC-Q100-certificering zal behalen. Bovendien zal TSMC ontwerpkits voor “Auto-Use” integreren binnen de PDK van N2P zodat klanten hun automotive-ontwikkelingen sneller kunnen starten.

Dit is bijzonder relevant omdat de geavanceerde automobieltechnologie, ADAS-systemen en wat men de “fysieke AI” noemt, op zoek zijn naar eerste-groep knooppunten met strengere betrouwbaarheidseisen. TSMC anticipeert hierop met een specifieke aanbod, niet enkel een late aanpassing van zijn consumentenknopen.

CoWoS, SoW-X en SoIC: de kern van de AI-strijd

Als de logische routekaart indruk maakt, zegt de pakketvorming-routekaart nog meer over de huidige stand van de industrie. TSMC bevestigde dat het al CoWoS van 5,5 reticles produceert en dat in 2028 die technologie zal uitbreiden naar 14 reticles. Hierdoor kunnen ongeveer 10 grote reken-chips en 20 HBM-stapelingen in één pakket worden geïntegreerd. In 2029 volgt een nog grotere versie met meer dan 14 reticles. Deze ontwikkelingen worden door TSMC gezien als een directe reactie op de behoefte om meer rekenkracht en geheugen te combineren in één package voor AI-belastingen.

Daarnaast ontwikkelt TSMC SoW-X, een wafer-omvattende systeemtechnologie die ook voor 2029 is gepland en gericht is op meer dan 40 reticles. Op het gebied van 3D-stapeling kondigde TSMC aan dat A14-to-A14 SoIC klaar zal zijn voor productie in 2029, met een die-naar-die E/S-dichtheid die 1,8 keer hoger ligt dan die van N2-on-N2 SoIC. Deze specificaties benadrukken dat in AI interne bandbreedte en fysieke nabijheid tussen dies cruciaal worden, net zo belangrijk als het procesknooppunt.

Intel en Samsung blijven meedoen, maar de lat ligt nu hoger

Het zou overdreven zijn te zeggen dat TSMC “alle hoop heeft uitgewist” voor Intel en Samsung. Beide blijven ambitieus. Intel Foundry houdt vast aan haar roadmap met Intel 18A, dat al klaar is voor klantenprojecten, en Intel 14A, met PowerDirect als doorontwikkeling van dezelfde achterzijde-voeding. Ook breidt Intel uit met 18A-P en 18A-PT. Samsung bevestigde in 2024 dat ze doorgaat met plannen voor productie op 2 nm in 2025 en 1,4 nm in 2027.

Wat TSMC met deze routekaart vooral doet, is de concurrentiekracht verder verhogen. Het is niet meer voldoende om een geavanceerd knooppunt te hebben of enige achterzijde-voeding te beloven. De markt verlangt ook grootschalige pakketvorming voor AI, duidelijke automotive-roadmaps, integratie met HBM en consistente ontwerpstrategie tussen generaties. In die bredere context blijft TSMC het meest veelzijdige en goed gecoördineerde systeemacteur.

Veelgestelde vragen

Wat heeft TSMC precies aangekondigd in zijn roadmap tot 2029?

TSMC heeft nieuwe ontwikkelingen gepresenteerd zoals N2U, A13, A12 en N2A, evenals vooruitgang in pakketvorming met CoWoS van 14 reticles, uitbreiding naar meer dan 14 reticles, SoW-X en A14-to-A14 SoIC.

Wat is het voordeel van A13 ten opzichte van A14?

TSMC zegt dat A13 een directe shrink van A14 is met een 6 % minder oppervlak, volledige compatibiliteit met ontwerpregels en verbeteringen in energie-efficiëntie en prestatie. Productie wordt gepland voor 2029.

Wat is N2U en waarom is het belangrijk?

N2U is een nieuwe variant van het 2 nm-platform die een 3-4 % snelheidsverbetering of een 8-10 % lager energieverbruik biedt ten opzichte van N2P, met een lichte verbetering in dichtheid. Het staat gepland voor 2028.

Laat TSMC Intel en Samsung niet achter met deze routekaart?

Niet definitief. Intel en Samsung volgen eigen ambitieuze plannen, maar de routekaart van TSMC versterkt haar leiderschap door het combineren van knooppunttechnologie, achterzijde-voeding, automotive en geavanceerde pakketvorming binnen één geïntegreerde strategie.

Bron: Toms Hardware en TSMC